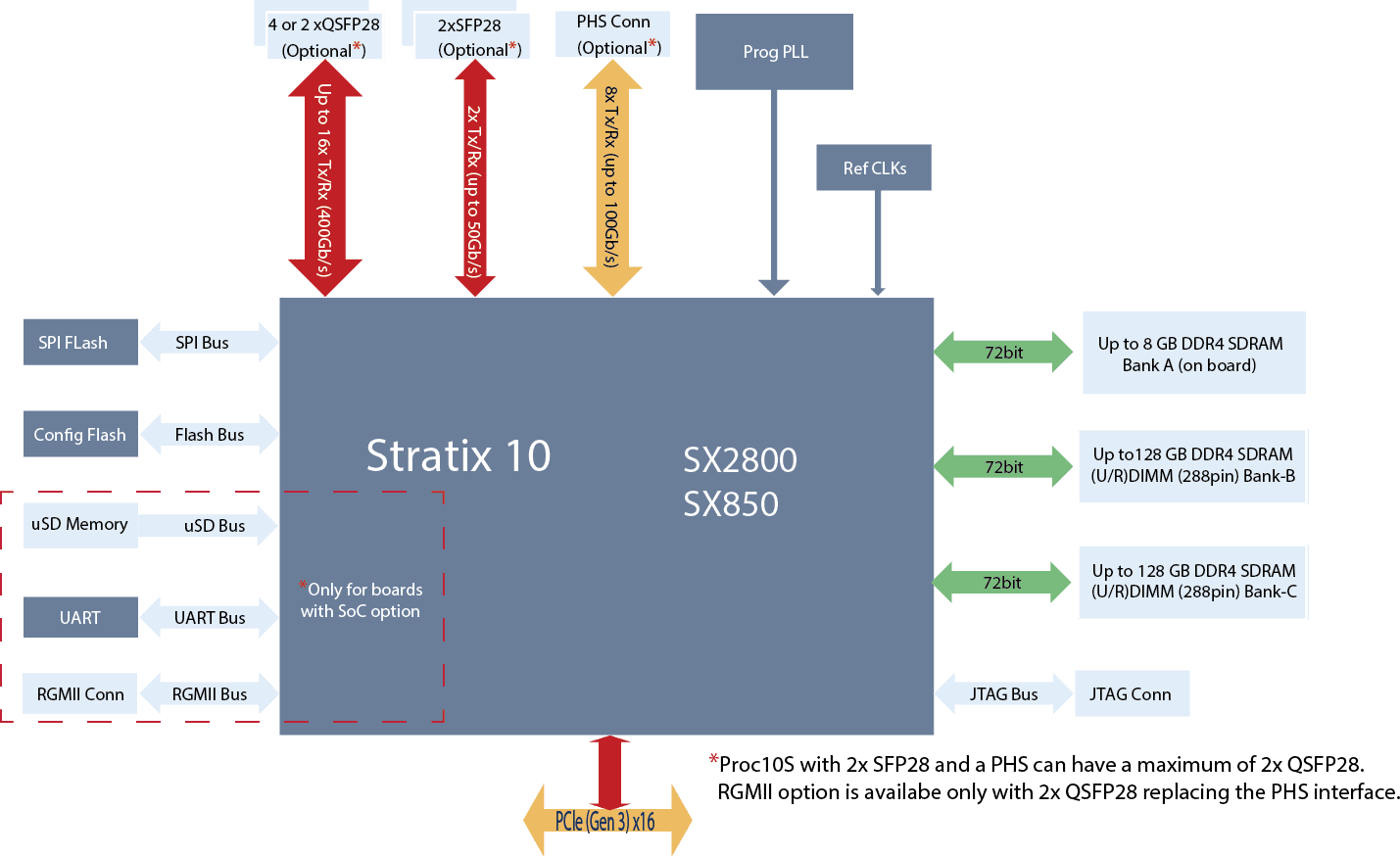

Gidel’s high-performance scalable FPGA computation accelerator, the Proc10S, pushes data processing power to new heights with peak single precision performance of up to 10 TFLOPS. The Proc10S features an Intel Stratix 10 FPGA with up to 2.8 million logic elements, 260 GB DDR4 memory, and an option for a SoC Quad-core 64-bit ARM Cortex-A53 MPCore processor.

The Proc10S boasts a 16-lane PCIe Gen. 3 host interface and 25/14.1 Gb/s SERDES I/O transceivers for ultra-fast connectivity to the FPGA. Abundant transceiver I/O connectivity enables a total of 400 Gb/s via 4xQSFP28 or a combination of 2xQSFP28, 2x SFP28 and RGMII/Gidel proprietary high-speed connector (PHS).

The Proc10S offers designers huge logic resources with incredible flexibility and performance capabilities to meet the most demanding design requirements. The Proc10S can address the design challenges of virtually all end markets, including HPC, storage, broadcast, medical, and test and measurement.

Application examples:

Specifications:

Up to 2,800K logic elements

H-TILE supporting up to 16x 25 Gb/s SERDES I/O

For SX devices, Quad-core 64 bit ARM Cortex-A53 MPCore processor

11,721 M20K (20K-bit) SRAM blocks

Up to 256 GB DDR4 SDRAM SoDIMM with throughput of up to 13.5 GB/s

4 GB on-board DDR4 SDRAM with throughput of up to 48 GB/s

Peak floating-point performance 9.2 TFLOPS

M20K blocks at up to 58 TB/s sustain access

Up to 11,520 18x19 variable precision multipliers

Up to 10x 25 Gb/s reconfigurable transceivers

Quad-core 64-bit ARM Cortex-A53 MPCore @ max processor speed of 1.5 GHz

Temperature monitoring

Internal voltage monitoring

Support for Partial Reconfiguration and CvP

Please contact us if you need a customized solution!

Options:

The Proc10S is supported by Gidel’s unique proprietary tools for developing on FPGA. These tools offer a solution that is unique in the market and can be used together with Intel’s design tools to achieve unmatched development efficiency and efficacy. The Gidel development tools suite simplifies significantly the hardware-software integration and offers powerful IPs for on-FPGA real-time data management and data compression.

- Gidel ProcDev Kit for HDL design flow and software application:

- Generation of environment FPGA code, including all board/IP constrains, interfaces, and user logic wrapper

- Generation of dedicated application driver and API support

- Splitting of physical on-board memories into logical memories with independent parallel access to/from user logic

- Intel Tools: Quartus Prime Pro, including QSys and DSP builder