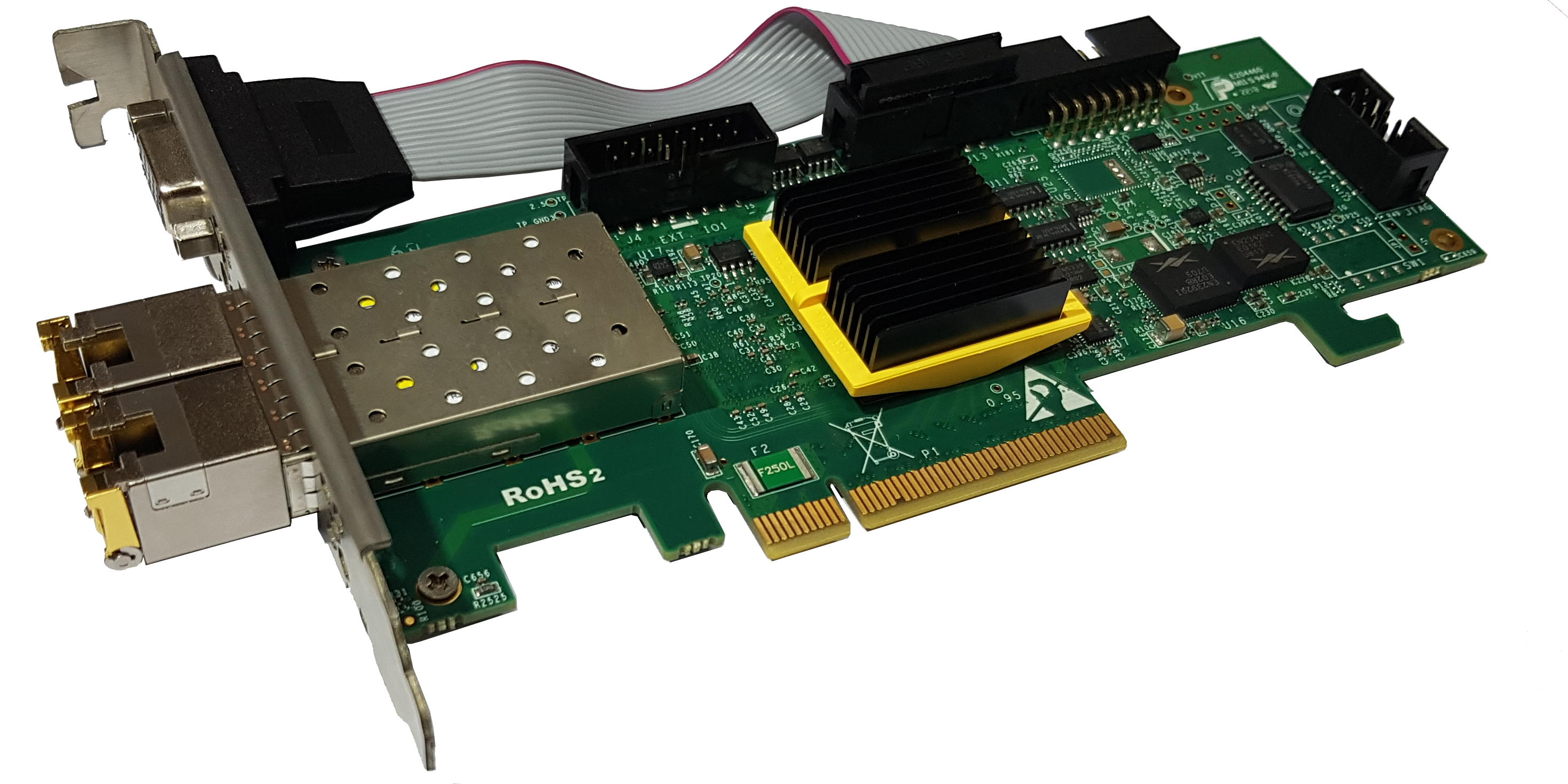

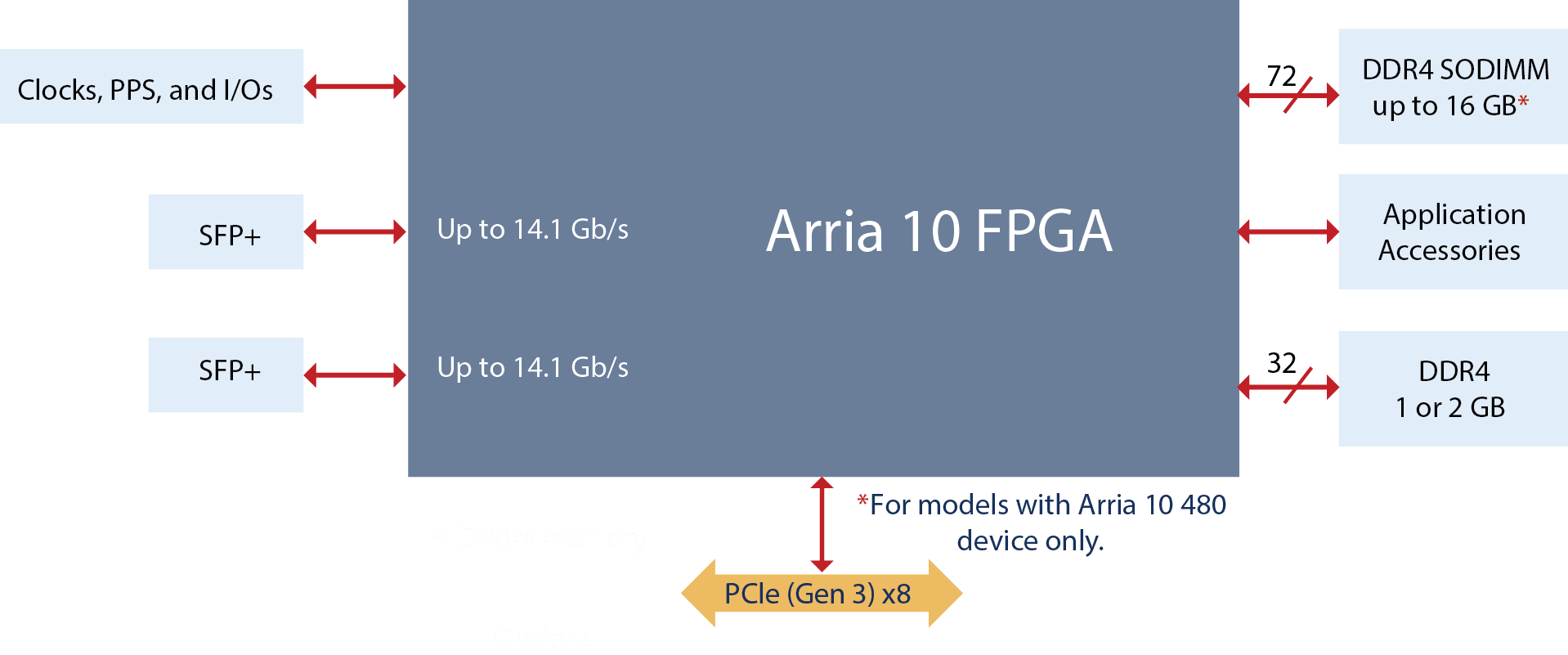

The HawkEye is a low-profile PCIe FPGA compute accelerator based on Intel’s Arria 10 FPGAs . The platform boasts up to 18 GB DDR4 on-board memory, 2 SFP+ links for a maximum of 28 Gb/s, and a PCIe x8 Gen. 3 host interface. The Arria 10 FPGA provides up to 480K LEs and IEEE floating-point capability. The HawkEye’s memory scheme is composed of embedded SRAM memory, 1-2 GB DDR4, and up to 16 GB of DDR4 SoDIMM (only for boards with 480 devices). The DDR memory may be accessed via up to 48 parallel ports simultaneously.

The HawkEye family includes an option for SoC Hard Processor System (HPS) based on Arria 10 SX devices with an embedded dual core ARM processor. The SoC boards are supported by a MicroSD memory card allowing storage of large program images for stand-alone mode.

The HawkEye accelerator board exhibits an impressive power efficiency, starting at less than 12W. The board is fortified by abundant I/O interface possibilities, including RS422, Opto-coupler, external clock, LVDS, LVTTL (3V), and 30V/0.9A output. The HawkEye can operate as a PCIe-based platform or as a stand-alone compute accelerator. The system has been designed for exceptional high reliability with an MTBF beyond 1 million hours.

Application examples:

Specifications:

160K or 480K logic elements

Embedded 18x19 multipliers

Embedded M20K and MLAB blocks

Up to 2x 12.5/14.1 Gb/s transceivers

1.6 Gb/s LVDS performance

SoC Hard Processor System (HPS) with an embedded dual core ARM processor

M20K (20K-bit) SRAM blocks

Up to 16 GB DDR4 SDRAM (SoDIMM)

Up to 2 GB on-board DDR4 SDRAM

Up to 2 GB DDR4 SDRAM for a total of 5.6 GB/s

Up to 16 GB DDR4 SDRAM for a total of 10.8 GB/s

Up to 2,736 18x19 multipliers

Opto-coupler

LVDS and LVTTL (3V)

30V/0.9A output driver

External clock

For availability of additional HawkEye models, including SoC, 2 GB on-board, and other FPGA speed grades, please contact Gidel Sales

Options:

The HawkEye is supported by Gidel’s unique proprietary tools for developing on FPGA. These tools offer a solution that is unique in the market and can be used together with Intel’s design tools to achieve unmatched development efficiency and efficacy.

Development Tools:

- Gidel ProcDev Kit for HDL design flow:

- Generation of environment FPGA code, including all board/IP constrains and user logic wrapper

- Generation of dedicated application driver with API support

- Splitting of physical on-board memories into logical memories with independent parallel access to/from user logic

- Intel Tools: Quartus Prime Pro, including QSys and DSP builder